![]()

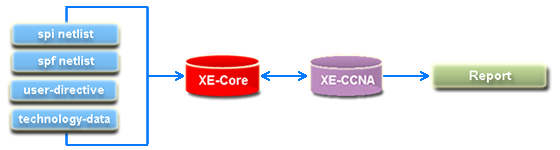

XE-CCNA (Capacitive Coupling Noise Analyzer) inputs a hierarchical schematic spice netlist and an extracted dspf netlist, automatically derives circuit properties for the analysis, and performs the analysis to reveal cross-talk noise issues that might result in electrical failures. XE-CCNA is capable of analyzing over 100M transistors and over 10GB extracted RC netlist within hours for a full-chip run and provides organized reports including netlist statistics, circuit classification properties, noise violations, and suggestions of design fixes.

XE inputs hierarchical spice netlist, automatically derives circuit analysis properties and logical equations for each net and transistor in the netlist, and stores these data in XE-Core engine. XE then back annotates post layout parasitics data onto XE-Core engine.

- Consistent pre-layout and post-layout analysis where the only differences are in parasitic values

- Hierarchical post-layout analysis where blackboxing the post-layout data of the lower level blocks

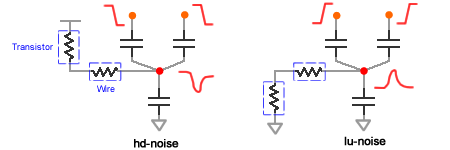

- Calculate 4 types of CCNs: high-up, low-up, high-down, low-down

- Noise tolerance on a victim net depends on its driver and receiver types.

- Calculate noise contribution from each individual aggressor. Defined by user-directives

- Calculate aggressor’s edge rates based on its driver Weff and load caps.

- Handle exclusive/complementary relations among aggressors and victim.

- Scripts available to automatically characterize technology data for CCNA.