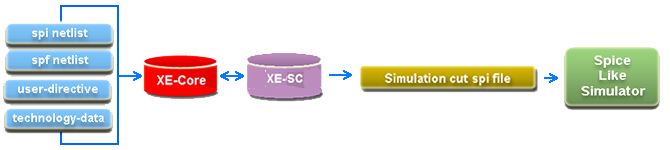

XE-SC (Simulation Cut) generates a Spice-simulatable netlist containing all paths between user specified start and end net(s). XE-SC inputs a hierarchical schematic spice netlist and an optional extracted dspf netlist, automatically derives circuit properties and logical equations for each net and transistor in the netlist, and stores these data in XE-Core engine. Designers use python and XE-SC's APIs to generates a spice deck containing all the paths between their specified start and end net(s). Unique sensitization output files can be optionally generated.

Some XE-SC features includes:

- Fast or slow cut path

- Auto sensitization

- Cap and Voltage Control Voltage Source side load model

- Prelayout netlist cut

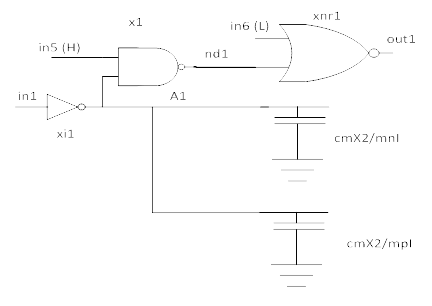

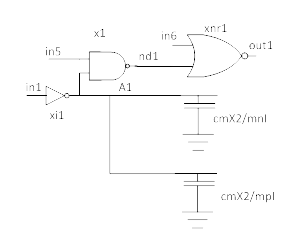

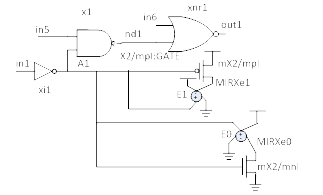

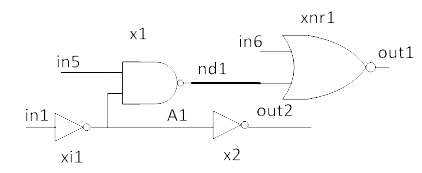

The following is an example of a simple nand-nor cut from in1 to out1. x2's transistors are modeled as side loads.

|

Cut with Capacitance side load

|

Cut with Voltage Control Voltage Source side load

|

With auto sensitization, XE-SC auto sensitizes in5 as high and in6 as low to ensure signal on in1 is propagated to out1.