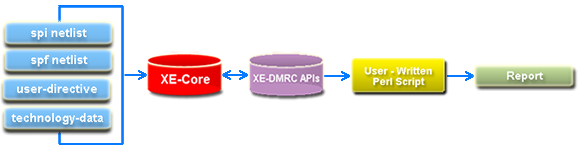

XE-DMRC (Design Methodology Rule Checker) allows you to create perl scripts to access XE-Core data and check your electrical design rules.

-

-

-

- A Perl script uses XE-DMRC APIs to obtain XE-Core circuit analysis properties, perform design checks, and report results.

- An optional spf file is processed to add layout RC data of each net and parasitic data of each transistor into XE-Core circuit analysis properties.

- User-directive file is processed to override the XE-Core circuit analysis properties.

The following electrical design rules had been coded and deployed:

- Edge rates/fan out check

- Output capacitance and driver strength check

- Dangling nodes check

- Beta ratios check

- Stack height check

- Serial pass devices check

- Cross-coupled structures check

- Dynamic-gate feedback structures check

- Latch feedback structures check

- Sense-amp transistor sizes check

- Ram-cell transistor sizes check

- Dynamic-gate usages check, dynamic Stage Check, general domino topology

|

- High/low Vth transistor usages check, supply check

- Clock skew check

- XY distance check

- Back to back latch check

- Device Hi_Vt usage check

- Max RC check

- Connection directly to main Vdd or Vss supply check

- Device size check

- Writability and feedback checks

- EM check

|

← XE-CKCXE-LM →

![]()