EDA Tools Provider

YX Technologies provides XE software to analyze and abstract complex VLSI circuits. With years of innovation and experience, we offer cutting-edge product to help and support design engineers to resolve the challenging difficulties for their complex chip designs.

![]()

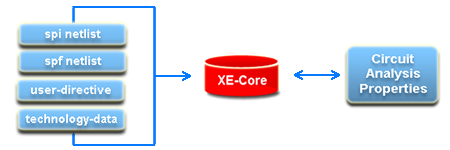

XE inputs a hierarchical spice netlist, automatically classifies and derives circuit properties and logical equations for each net and transistor in the netlist, and stores these data in XE-Core engine. XE then back-annotates post-layout parasitics data into XE-Core engine . A typical netlist accepted by XE represents a complex, hierarchical custom circuit with transistors, diodes, capacitors and resistors.

![]()

- XE is a Xtor (Transistor) Engine for a static analysis.

- XE is a transistor-level tool for full-custom circuit design methodology that can perform static circuit checks, generate abstract verilog model, and generate spice deck to simulate circuit check reported issues.

- XE emulates a circuit designer's analysis methodology, such as back-of-the-envelop calculations or creating small circuits to model and simulate the uncovered circuit issues.

- XE automatically classify circuits using a rule-based approach to derive circuit properties and abstraction equations.

- XE's Perl APIs for a perl-script implements circuit checks by accessing various circuit properties such as design hierarchies, CCRs (channel-connected region), pin directions, device sizes, net properties, and parasitics RC values, and other related information.

- XE utilizes C++ native applications to analyze complicate circuit problems.

- XE can handle mixed-mode design including passive devices such as diodes, resistors, and capacitors by providing various ways for user to indicate analog xtors while auto-classify limits number of common analog circuit families.

- XE can analyze over 100M transistors and over 10GB extracted RC netlists within few hours of run-time.

- XE has co-existing hierarchical and flat design data models. It can use pre-layout estimated RC if post-layout RC data is not available.

- XE provides customized report that can includes netlist statistics, classified and unclassified circuits, and all circuit problems found for each user requested check. XE also produce a log file with lists of problems encountered during the run. XE offers the flexibility to customers by providing a user-directive. It allows customers to overwrite default XE tool setting based on customers' design requirement.

- XE is an all in one static analysis product with comprehensive classify engine that requires no additional information beside tech file, user directives, netlist and physical information.

![]()

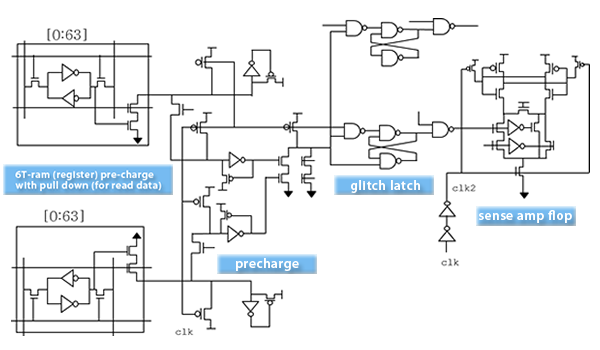

XE-Core engine automatically generates circuit analysis properties:

- Design hierarchies and sub-circuit pin directions

- Net properties include driver type, feedback driver type, receiver type, channel-connected region, effective width, clock and scan types, resistances and capacitances.

- Transistor properties include circuit family type, signal flow direction, only-for-feedback usage, on scan-chain, only virtual-ground usage, physical dimensions, and device capacitances.

![]()

Transistors: sense amp flop, 6T-ram, pull-down, pull-up, weak-feedback, inverter

Nets: wordline, bitline, ram-stored, precharge, inverter

Capacitance: on each transistor or net

Resistance: on each net

Circuit hierarchies

![]()

- XE-CCNA (Capacitive Coupling Noise Analyzer)

- XE-CCNASC (Capacitive Coupling Noise Analysis Simulation Cut)

- XE-CKC (Circuit Checker)

- XE-DMRC (Design Methodology Rules Checker)

- XE-LM (Logic Modeler)

- XE-SC (Simulation Cut)